SoC (Chip on System) we SiP (Package System) ikisi hem häzirki zaman integral zynjyrlary ösdürmekde möhüm ähmiýete eýe bolup, miniatýurizasiýa, netijelilik we elektron ulgamlaryň integrasiýasyna mümkinçilik berýär.

1. SoC we SiP-iň kesgitlemeleri we esasy düşünjeleri

SoC (Çipdäki ulgam) - Bütin ulgamy bir çipe birleşdirmek

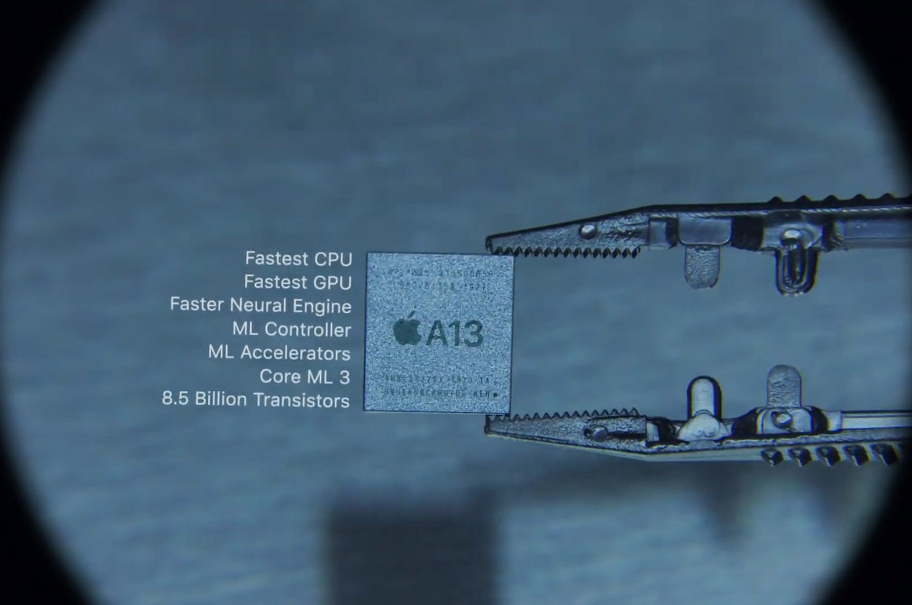

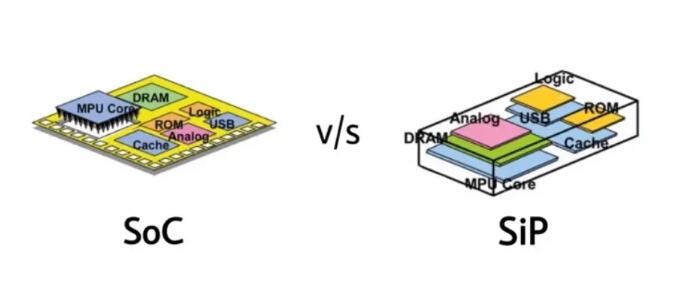

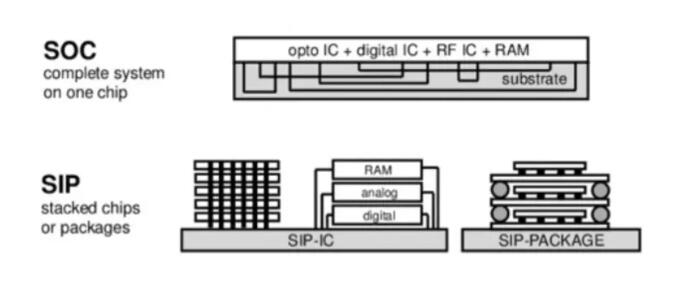

SoC, ähli funksional modullar birmeňzeş fiziki çipe birleşdirilen we birleşdirilen gök binalara meňzeýär. SoC-iň esasy pikiri, elektron ulgamynyň ähli esasy komponentlerini, şol sanda prosessor (CPU), ýat, aragatnaşyk modullary, analog zynjyrlar, datçik interfeýsleri we beýleki dürli funksional modullary bir çipe birleşdirmekdir. SoC-iň artykmaçlyklary ýokary integrasiýa derejesinde we kiçi göwrümde bolup, öndürijilikde, energiýa sarp edilişinde we ölçeglerinde ep-esli artykmaçlyklary üpjün edýär, bu bolsa ýokary öndürijilikli, kuwwata duýgur önümler üçin aýratyn amatly bolýar. “Apple” smartfonlaryndaky prosessorlar “SoC” çipleriniň mysalydyr.

Mysal üçin, SoC ähli funksiýalaryň içinde işlenip düzülen we dürli funksional modullar dürli gatlara meňzeýän şäherdäki "super bina" meňzeýär: käbirleri ofis meýdançalary (prosessorlar), käbiri güýmenje meýdançalary (ýat), käbirleri aragatnaşyk ulgamlary (aragatnaşyk interfeýsleri), hemmesi bir binada (çip) jemlenendir. Bu, tutuş ulgamyň has ýokary netijelilige we öndürijilige ýetip, bir kremniy çipde işlemegine mümkinçilik berýär.

SiP (Paketdäki ulgam) - Dürli çipleri birleşdirmek

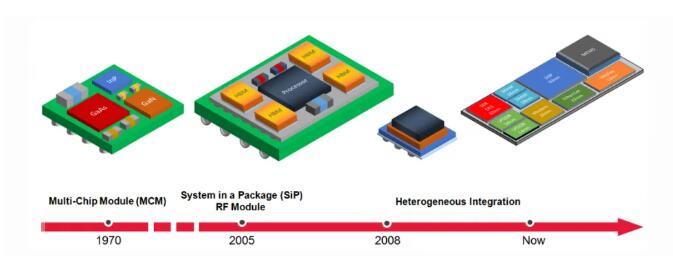

SiP tehnologiýasynyň çemeleşmesi başga. Birmeňzeş fiziki paketiň içinde dürli funksiýaly birnäçe çipi gaplamaga meňzeýär. SoC ýaly bir çipe birikdirmek däl-de, gaplamak tehnologiýasy arkaly birnäçe funksional çipleri birleşdirmäge ünsi jemleýär. SiP birnäçe çipleri (prosessorlar, ýat, RF çipleri we ş.m.) gapdal gaplamaga ýa-da şol bir modulyň içinde saklamaga mümkinçilik berýär we ulgam derejesinde çözgüt döredýär.

SiP düşünjesini gural gutusyny ýygnamak bilen deňeşdirip bolar. Gurallar gutusy tornavida, çekiç we buraw ýaly dürli gurallary öz içine alyp biler. Garaşsyz gurallar bolsa-da, amatly ulanmak üçin hemmesi bir gutuda jemlenendir. Bu çemeleşmäniň peýdasy, her bir guralyň aýratyn işlenip düzülmegi we öndürilmegi we çeýeligi we tizligi üpjün edip, zerur bolanda ulgam bukjasyna "ýygnalyp" bolmagydyr.

2. Tehniki aýratynlyklar we SoC bilen SiP arasyndaky tapawutlar

Integrasiýa usulynyň tapawutlary:

SoC: Dürli funksional modullar (CPU, ýat, I / O we ş.m.) şol bir kremniniň çipinde gönüden-göni işlenip düzüldi. Modhli modullar bitewi ulgamy emele getirip, birmeňzeş prosesi we dizaýn logikasyny paýlaşýarlar.

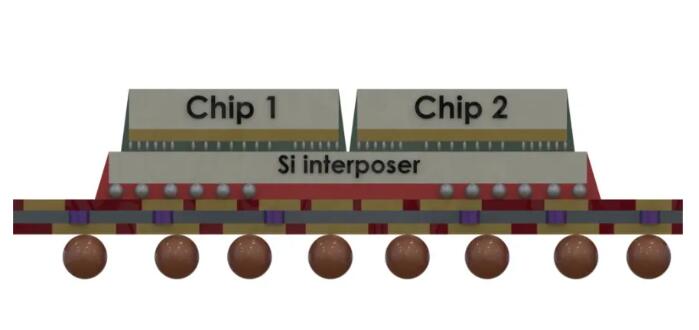

SiP: Dürli funksiýaly çipler dürli amallary ulanyp öndürilip, soňra fiziki ulgam döretmek üçin 3D gaplama tehnologiýasy arkaly bir gaplama modulynda birleşdirilip bilner.

Dizaýn çylşyrymlylygy we çeýeligi:

SoC: modhli modullar bir çipde birleşdirilendigi sebäpli dizaýn çylşyrymlylygy gaty ýokary, esasanam sanly, analog, RF we ýat ýaly dürli modullaryň bilelikdäki dizaýny üçin. Munuň üçin inersenerleriň çuňňur domen dizaýn mümkinçiliklerine eýe bolmagy talap edilýär. Mundan başga-da, SoC-de haýsydyr bir modul bilen dizaýn meselesi bar bolsa, ep-esli töwekgelçilik döredýän ähli çipi täzeden dizaýn etmeli bolup biler.

SiP: Munuň tersine, SiP has uly dizaýn çeýeligini hödürleýär. Dürli funksional modullar ulgama gaplanmazdan ozal aýratyn dizaýn edilip we barlanyp bilner. Modul bilen bir mesele ýüze çyksa, beýleki bölekleri täsirsiz galdyryp, diňe şol moduly çalyşmaly. Şeýle hem bu, SoC bilen deňeşdirilende has çalt ösüş tizligini we pes töwekgelçiligi üpjün edýär.

Amallaryň laýyklygy we kynçylyklary:

SoC: Sanly, analog we RF ýaly dürli funksiýalary bir çipe birikdirmek, prosesiň utgaşmagynda möhüm kynçylyklar bilen ýüzbe-ýüz bolýar. Dürli funksional modullar dürli önümçilik amallaryny talap edýär; mysal üçin sanly zynjyrlara ýokary tizlikli, pes güýçli prosesler gerek, analog zynjyrlar bolsa has takyk naprýa controleniýäni talap edip biler. Şol bir çipdäki bu dürli prosesleriň arasynda utgaşyklygy gazanmak gaty kyn.

SiP: Gaplamak tehnologiýasy arkaly, SiP dürli prosesleri ulanyp öndürilen çipleri birleşdirip, SoC tehnologiýasy bilen ýüzbe-ýüz bolýan prosesiň utgaşyklyk meselelerini çözüp biler. SiP birnäçe birmeňzeş çipleriň bir paketde bilelikde işlemegine mümkinçilik berýär, ýöne gaplamak tehnologiýasy üçin takyk talaplar ýokary.

Gözleg we gözleg sikli we çykdajylary:

SoC: SoC ähli modullary noldan dizaýn etmegi we barlamagy talap edýändigi sebäpli, dizaýn sikli has uzyn. Her modul berk dizaýn, tassyklama we synagdan geçmeli we umumy ösüş prosesi birnäçe ýyl dowam edip biler, bu bolsa köp çykdajylara sebäp bolar. Şeýle-de bolsa, köpçülikleýin önümçilikde bir gezek ýokary integrasiýa sebäpli birligiň bahasy arzan bolýar.

SiP: Gözleg we gözleg sikli SiP üçin has gysga. SiP gaplamak üçin bar bolan, barlanan funksional çipleri gönüden-göni ulanýandygy sebäpli, modulyň täzeden dizaýn edilmegi üçin zerur wagty azaldýar. Bu önümiň has çalt çykarylmagyna mümkinçilik döredýär we gözleg we barlag çykdajylaryny ep-esli peseldýär.

Ulgam öndürijiligi we ululygy:

SoC: modhli modullar bir çipde bolany üçin, aragatnaşyk gijikdirilmegi, energiýa ýitgileri we signal päsgelçiligi azaldylýar, bu bolsa SoC-a öndürijilik we energiýa sarp etmekde deňi-taýy bolmadyk artykmaçlyk berýär. Onuň göwrümi minimal bolup, smartfonlar we şekili gaýtadan işlemek çipleri ýaly ýokary öndürijilikli we güýç talaplary bolan programmalar üçin aýratyn amatly bolýar.

SiP: SiP-iň integrasiýa derejesi SoC-den ýokary bolmasa-da, köp gatlakly gaplama tehnologiýasy arkaly dürli çipleri ykjam gaplap bilýär, netijede adaty köp çipli çözgütler bilen deňeşdirilende has kiçi göwrüm bolýar. Mundan başga-da, modullar şol bir kremniy çipde birleşdirilmän, fiziki taýdan gaplananlygy sebäpli, öndürijilik SoC-iňki bilen gabat gelmeýänligi sebäpli, köp programmalaryň isleglerini kanagatlandyryp biler.

3. SoC we SiP üçin amaly ssenariler

SoC üçin amaly ssenariýler:

SoC, adatça ululygy, güýji sarp etmek we öndürijilik üçin ýokary talaplary bolan meýdanlar üçin amatlydyr. Mysal üçin:

Smartfonlar: Smartfonlardaky prosessorlar (“Apple” -iň “A” seriýaly çipleri ýa-da “Qualcomm” -yň “Snapdragon”) adatça ýokary öndürijilikli we pes energiýa sarp etmegi talap edýän CPU, GPU, AI gaýtadan işleýän bölümleri, aragatnaşyk modullaryny we ş.m. öz içine alýan ýokary integrirlenen SoC-lerdir.

Suraty gaýtadan işlemek: Sanly kameralarda we dronlarda şekili gaýtadan işleýän bölümler köplenç güýçli paralel gaýtadan işlemek mümkinçiliklerini we SoC-iň netijeli gazanyp biljek pes gijä galmagyny talap edýär.

Perokary öndürijilikli oturdylan ulgamlar: SoC, IoT enjamlary we geýilýän zatlar ýaly berk energiýa netijeliligi talaplary bolan kiçi enjamlar üçin has amatlydyr.

SiP üçin amaly ssenariler:

SiP, çalt ösüşi we köp funksiýaly integrasiýany talap edýän meýdanlar üçin amatly programma ssenarileriniň has giň toplumyna eýedir:

Aragatnaşyk enjamlary: Esasy stansiýalar, marşrutizatorlar we ş.m. üçin SiP önümiň ösüş siklini çaltlaşdyryp, birnäçe RF we sanly signal prosessorlaryny birleşdirip biler.

Sarp ediji elektronikasy: Çalt täzeleniş siklleri bolan akylly sagatlar we Bluetooth nauşnikleri ýaly önümler üçin SiP tehnologiýasy täze aýratynlyk önümleriniň has çalt çykarylmagyna mümkinçilik berýär.

Awtoulag elektronikasy: Awtoulag ulgamlaryndaky dolandyryş modullary we radar ulgamlary dürli funksional modullary çalt birleşdirmek üçin SiP tehnologiýasyny ulanyp biler.

4. SoC we SiP-iň geljekki ösüş meýilleri

SoC ösüşiniň tendensiýalary:

SoC, AI prosessorlarynyň, 5G aragatnaşyk modullarynyň we beýleki funksiýalaryň has köp integrasiýasyny öz içine alýan has ýokary integrasiýa we birmeňzeş integrasiýa tarap ösmegini dowam etdirer, akylly enjamlaryň mundan beýläk-de ewolýusiýasyna itergi berer.

SiP ösüşiniň tendensiýalary:

SiP, çalt üýtgeýän bazar isleglerini kanagatlandyrmak üçin dürli amallar we funksiýalar bilen çipleri berk gaplamak üçin 2.5D we 3D gaplama öňe gidişligi ýaly ösen gaplama tehnologiýalaryna has köp bil baglar.

5. Netije

SoC, ähli funksional modullary bir dizaýnda jemläp, öndürijilik, ululyk we güýç sarp etmek üçin gaty ýokary talaplary bolan programmalar üçin köp funksiýaly super gök bina gurmak ýalydyr. Beýleki tarapdan, SiP, çeýe we çalt ösüşe has köp üns berýän, esasanam çalt täzelenmegi talap edýän sarp ediş elektronikasy üçin amatly bolan dürli funksional çipleri ulgama "gaplamak" ýalydyr. Ikisiniňem güýçli taraplary bar: SoC ulgamyň optimal işleýşine we ululygynyň optimizasiýasyna ünsi çekýär, SiP bolsa ulgamyň çeýeligini we ösüş sikliniň optimizasiýasyny görkezýär.

Iş wagty: 28-2024-nji oktýabr