SoC (Çipdäki ulgam) we SiP (Paketdäki ulgam) elektron ulgamlarynyň kiçileşdirilmegine, netijeliligine we integrasiýasyna mümkinçilik berýän döwrebap integral mikroshemalaryň ösüşinde möhüm tapgyrlardyr.

1. SoC we SiP-iň kesgitlemeleri we esasy düşünjeleri

SoC (Çipdäki Sistema) - Tutuş ulgamy bir çipe integrasiýa etmek

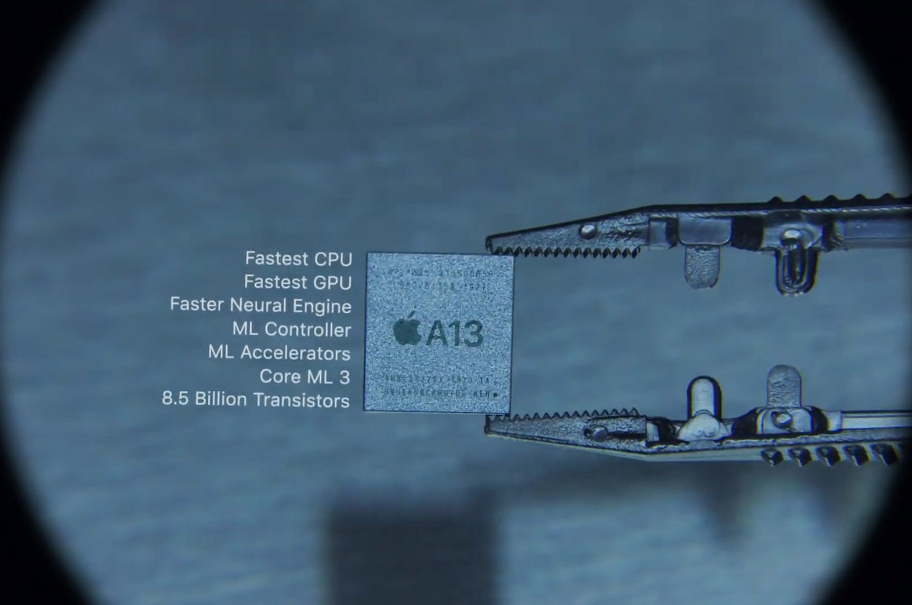

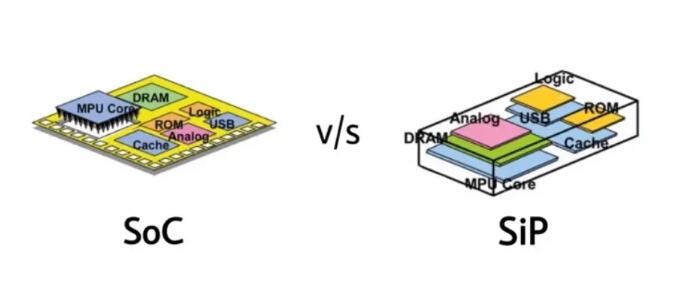

SoC gökdelen ýalydyr, bu ýerde ähli funksional modullar bir fiziki çipe dizaýn edilip, birleşdirilendir. SoC-iň esasy ideýasy elektron ulgamyň ähli esasy böleklerini, şol sanda prosessory (CPU), ýatda saklamany, aragatnaşyk modullaryny, analog zynjyrlary, sensor interfeýslerini we beýleki dürli funksional modullary bir çipe birleşdirmekdir. SoC-iň artykmaçlyklary onuň ýokary derejede integrasiýasynda we kiçi ölçeginde bolup, öndürijilikde, energiýa sarp edilişinde we ölçeglerinde uly artykmaçlyklary üpjün edýär, bu bolsa ony ýokary öndürijilikli, energiýa duýgur önümler üçin has amatly edýär. Apple smartfonlaryndaky prosessorlar SoC çipleriniň mysallarydyr.

Mysal üçin, SoC şäherdäki "super bina" ýalydyr, bu ýerde ähli funksiýalar öz içine dizaýn edilýär we dürli funksional modullar dürli gatlar ýalydyr: käbirleri ofis meýdançalary (prosessorlar), käbirleri güýmenje meýdançalary (ýat) we käbirleri aragatnaşyk ulgamlary (aragatnaşyk interfeýsleri) bolup, bularyň hemmesi bir binada (çip) jemlenendir. Bu bolsa tutuş ulgamyň bir kremniý çipinde işlemegine mümkinçilik berýär we has ýokary netijeliligi we öndürijiligi gazanýar.

SiP (Paketdäki Sistema) - Dürli çipleri bir ýere jemlemek

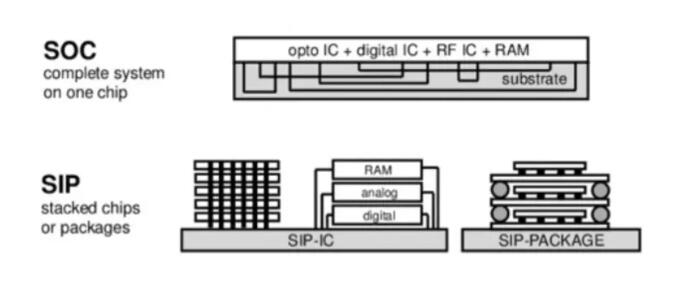

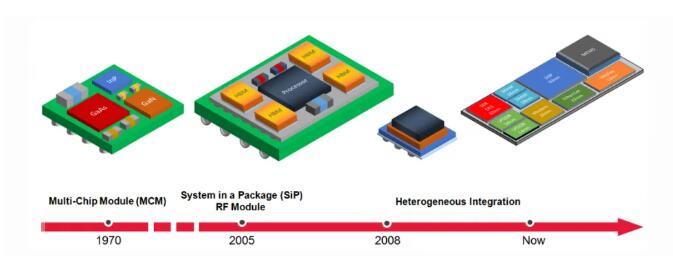

SiP tehnologiýasynyň çemeleşmesi başgaça. Ol bir fiziki bukjada dürli funksiýalary bolan birnäçe çipi gaplamaga has meňzeýär. Ol SoC ýaly bir çipe integrasiýa etmekden has köp, birnäçe funksiýaly çipleri gaplama tehnologiýasy arkaly birleşdirmäge ünsi jemleýär. SiP birnäçe çipleriň (prosessorlar, ýat, RF çipleri we ş.m.) ýan-ýana gaplanmagyna ýa-da bir modulyň içinde üst-üste goýulmagyna mümkinçilik berýär we ulgam derejesindäki çözgüdi emele getirýär.

SiP konsepsiýasyny gurallar gutusyny ýygnamaga meňzetmek bolar. Gurallar gutusynda otwertkalar, çekiçler we burgular ýaly dürli gurallar bolup biler. Olar garaşsyz gurallar bolsa-da, amatly ulanmak üçin hemmesi bir gutuda jemlenendir. Bu çemeleşmäniň peýdasy, her bir guraly aýratynlykda işläp we öndürip bolýar, şeýle hem olary zerur bolanda ulgam toplumyna "ýygnap" bolýar, bu bolsa çeýeligi we tizligi üpjün edýär.

2. SoC we SiP arasyndaky tehniki häsiýetnamalar we tapawutlar

Integrasiýa usullarynyň tapawutlary:

SoC: Dürli funksional modullar (prosessor, ýat, giriş/çykyş we ş.m.) gönüden-göni şol bir kremniý çipinde dizaýn edilýär. Ähli modullar birmeňzeş esasy prosessi we dizaýn logikasyny paýlaşýar we bitewi ulgamy emele getirýär.

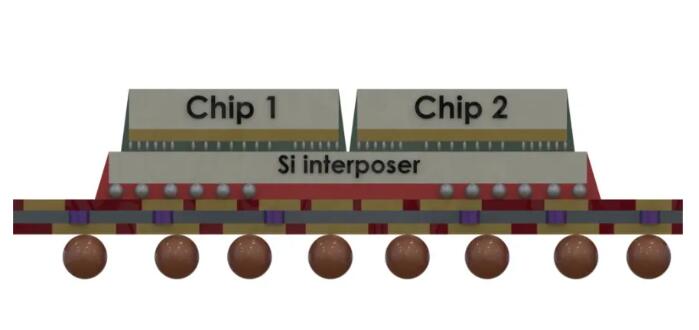

SiP: Dürli funksional çipler dürli prosesler arkaly öndürilip, soňra fiziki ulgamy döretmek üçin 3D gaplama tehnologiýasyny ulanyp ýeke-täk gaplama modulynda birleşdirilip bilner.

Dizaynyň çylşyrymlylygy we çeýeligi:

SoC: Ähli modullar bir çipde birleşdirilendigi sebäpli, dizaýn çylşyrymlylygy örän ýokary, esasanam sanly, analog, RF we ýat ýaly dürli modullaryň bilelikdäki dizaýny üçin. Bu inženerlerden çuňňur köpugurly dizaýn mümkinçiliklerine eýe bolmagy talap edýär. Mundan başga-da, SoC-däki islendik modul bilen dizaýn meselesi ýüze çyksa, tutuş çip täzeden işlenip düzülmeli bolup biler, bu bolsa uly töwekgelçilikleri döredýär.

SiP: Tersine, SiP has uly dizaýn çeýeligini hödürleýär. Dürli funksional modullar ulgama gaplanmazdan öň aýratynlykda dizaýn edilip we barlanyp bilner. Eger modul bilen mesele ýüze çyksa, diňe şol moduly çalşyrmak gerek, beýleki bölekleri täsirlenmez. Bu, şeýle hem, SoC bilen deňeşdirilende has çalt işläp düzmek tizligini we töwekgelçilikleri azaltmaga mümkinçilik berýär.

Prosesleriň utgaşyklylygy we kynçylyklary:

SoC: Sanly, analog we RF ýaly dürli funksiýalary bir çipe goşmak prosesleriň utgaşyklylygynda uly kynçylyklara duçar bolýar. Dürli funksional modullar dürli önümçilik proseslerini talap edýär; mysal üçin, sanly zynjyrlar ýokary tizlikli, pes kuwwatly prosesleri talap edýär, analog zynjyrlar bolsa has takyk naprýaženiýe gözegçiligini talap edip biler. Şol bir çipde bu dürli prosesleriň arasynda utgaşyklylyga ýetmek örän kyn.

SiP: Gaplama tehnologiýasy arkaly SiP dürli prosesleri ulanyp öndürilen çipleri birleşdirip, SoC tehnologiýasynyň ýüzbe-ýüz bolýan proses utgaşyklylygy bilen baglanyşykly meseleleri çözüp bilýär. SiP birnäçe dürli çipleriň bir gaplamada bilelikde işlemegine mümkinçilik berýär, ýöne gaplama tehnologiýasy üçin takyklyk talaplary ýokarydyr.

Ylmy-barlag we işläp düzme işleriniň sikli we çykdajylary:

SoC: SoC ähli modullary başdan dizaýn etmegi we barlamagy talap edýändigi sebäpli, dizaýn sikli has uzak bolýar. Her bir modul berk dizaýndan, barlamadan we synagdan geçmeli we umumy işläp düzmek prosesi birnäçe ýyl dowam edip biler, bu bolsa ýokary çykdajylara sebäp bolup biler. Şeýle-de bolsa, köpçülikleýin önümçilik başlanandan soň, ýokary integrasiýa sebäpli birligiň bahasy arzan bolýar.

SiP: SiP üçin ylmy-barlag we işläp taýýarlama sikli has gysga. SiP gaplamak üçin bar bolan, tassyklanan funksional çipleri gönüden-göni ulanýandygy sebäpli, modulyň täzeden dizaýn edilmegi üçin gerek bolan wagty azaldýar. Bu önümiň has çalt çykarylmagyna mümkinçilik berýär we ylmy-barlag we işläp taýýarlama çykdajylaryny ep-esli azaldýar.

Sistemanyň öndürijiligi we ölçegi:

SoC: Ähli modullar bir çipde ýerleşýändigi sebäpli, aragatnaşyk gijikmeleri, energiýa ýitgileri we signal päsgelçilikleri iň pes derejä düşürilýär, bu bolsa SoC-a öndürijilik we energiýa sarp edilişi babatda deňsiz-taýsyz artykmaçlyk berýär. Onuň ölçegi minimal, bu bolsa ony smartfonlar we surat işleme çipleri ýaly ýokary öndürijilik we energiýa talaplary bolan programmalar üçin has amatly edýär.

SiP: SiP-iň integrasiýa derejesi SoC-iňki ýaly ýokary bolmasa-da, ol köp gatlakly gaplama tehnologiýasyny ulanyp dürli çipleri bilelikde ýygjam gaplap bilýär, bu bolsa däp bolan köp çipli çözgütlere garanyňda has kiçi ölçegli bolýar. Mundan başga-da, modullar bir kremniý çipine integrasiýa edilmän, fiziki taýdan gaplananlygy sebäpli, öndürijilik SoC-iňki bilen deň gelmese-de, ol köp programmalaryň zerurlyklaryny kanagatlandyryp bilýär.

3. SoC we SiP üçin ulanylyş ssenarileri

SoC üçin ulanylyş senariýleri:

SoC, adatça, ölçeg, energiýa sarp edilişi we öndürijilik boýunça ýokary talaplary bolan meýdanlar üçin amatlydyr. Mysal üçin:

Smartfonlar: Smartfonlardaky prosessorlar (meselem, Apple-iň A seriýaly çipleri ýa-da Qualcomm-yň Snapdragon-y) adatça ýokary derejede integrasiýa edilen SoC-ler bolup, olar prosessory, GPU, AI işläp düzüji bloklary, aragatnaşyk modullary we ş.m. öz içine alýar we güýçli öndürijiligi we az energiýa sarp edilişini talap edýär.

Surat işlemegi: Sanly kameralarda we dronlarda surat işlemegiň enjamlary köplenç güýçli parallel işlemegiň mümkinçiliklerini we pes gijikmäni talap edýär, SoC bolsa muňa netijeli ýetip bilýär.

Ýokary öndürijilikli ornaşdyrylan ulgamlar: SoC, esasanam, IoT enjamlary we geýilýän enjamlar ýaly energiýa netijeliligi boýunça berk talaplary bolan kiçi enjamlar üçin amatlydyr.

SiP üçin ulanylyş senariýleri:

SiP-iň has giň ulanyş senariýleri bar, olar çalt ösüşi we köp funksiýaly integrasiýany talap edýän ugurlar üçin amatlydyr, mysal üçin:

Aragatnaşyk enjamlary: Baza stansiýalary, routerler we ş.m. üçin SiP önümiň işlenip düzüliş siklini çaltlaşdyryp, birnäçe RF we sanly signal prosessorlaryny birleşdirip bilýär.

Sarp ediji elektronikasy: Çalt täzelenme siklleri bolan akylly sagatlar we Bluetooth garnituralar ýaly önümler üçin SiP tehnologiýasy täze aýratynlyk önümleriniň has çalt çykarylmagyna mümkinçilik berýär.

Awtomobil elektronikasy: Awtomobil ulgamlaryndaky dolandyryş modullary we radar ulgamlary dürli funksional modullary çalt birleşdirmek üçin SiP tehnologiýasyny ulanyp bilerler.

4. SoC we SiP-niň geljekki ösüş meýilleri

SoC ösüşinde tendensiýalar:

SoC has ýokary integrasiýa we dürli integrasiýa tarap ösüşini dowam etdirer, mümkin bolsa AI prosessorlarynyň, 5G aragatnaşyk modullarynyň we beýleki funksiýalaryň has köp integrasiýasyny öz içine alar we bu bolsa akylly enjamlaryň has-da ösmegine itergi berer.

SiP ösüşinde tendensiýalar:

SiP, çalt üýtgeýän bazar talaplaryny kanagatlandyrmak üçin dürli prosesleri we funksiýalary bolan çipleri berk gaplamak üçin 2.5D we 3D gaplama ösüşleri ýaly ösen gaplama tehnologiýalaryna barha köp daýanar.

5. Netije

SoC, ähli funksional modullary bir dizaýna jemleýän, öndürijilik, ölçeg we energiýa sarp edilişi üçin örän ýokary talaplary bolan ulanylyşlar üçin amatly bolan köpugurly super gökdelen gurmaga has meňzeýär. Beýleki tarapdan, SiP, dürli funksional çipleri ulgama "gaplamak" ýalydyr, has köp çeýelige we çalt ösüşe, esasanam çalt täzelenmeleri talap edýän sarp ediji elektronika üçin amatlylyga ünsi jemleýär. Ikisiniň hem güýçli taraplary bar: SoC optimal ulgam öndürijiligine we ölçeg optimizasiýasyna ünsi çekýär, SiP bolsa ulgam çeýeligine we ösüş sikliniň optimizasiýasyna ünsi çekýär.

Ýerleşdirilen wagty: 2024-nji ýylyň 28-nji oktýabry